- 您现在的位置:买卖IC网 > Sheet目录3833 > AT80C51RA2-3CSUM (Atmel)IC 8051 MCU ROMLESS 40DIP

dsPIC33FJ32GP302/304,

dsPIC33F

J64GPX02/

X04,

AND

dsPIC

33FJ128GPX02/X04

DS70292G-p

age

48

2007-

2012

Microchip

T

echnolo

gy

Inc.

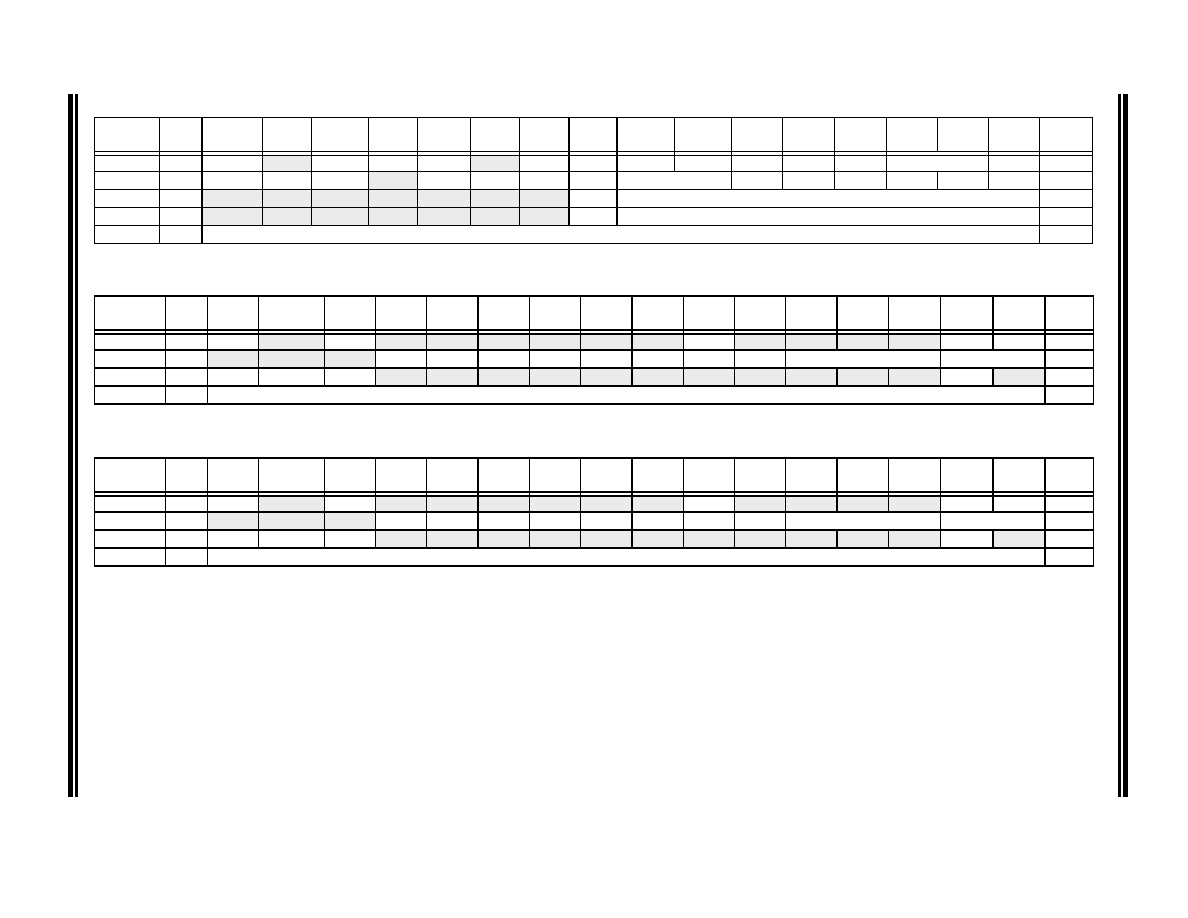

TABLE 4-10:

UART2 REGISTER MAP

SFR Name

SFR

Addr

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

All

Resets

U2MODE

0230

UARTEN

—

USIDL

IREN

RTSMD

—

UEN1

UEN0

WAKE

LPBACK

ABAUD

URXINV

BRGH

PDSEL<1:0>

STSEL

0000

U2STA

0232

UTXISEL1

UTXINV UTXISEL0

—

UTXBRK

UTXEN

UTXBF

TRMT

URXISEL<1:0>

ADDEN

RIDLE

PERR

FERR

OERR

URXDA

0110

U2TXREG

0234

—

UTX8

UART Transmit Register

xxxx

U2RXREG

0236

—

URX8

UART Receive Register

0000

U2BRG

0238

Baud Rate Generator Prescaler

0000

Legend:

x = unknown value on Reset, — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

TABLE 4-11:

SPI1 REGISTER MAP

SFR Name

SFR

Addr

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

All

Resets

SPI1STAT

0240

SPIEN

—

SPISIDL

—

—SPIROV

—

SPITBF

SPIRBF

0000

SPI1CON1

0242

—

DISSCK

DISSDO MODE16

SMP

CKE

SSEN

CKP

MSTEN

SPRE<2:0>

PPRE<1:0>

0000

SPI1CON2

0244

FRMEN

SPIFSD

FRMPOL

—

FRMDLY

—

0000

SPI1BUF

0248

SPI1 Transmit and Receive Buffer Register

0000

Legend:

x = unknown value on Reset, — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

TABLE 4-12:

SPI2 REGISTER MAP

SFR Name

SFR

Addr

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

All

Resets

SPI2STAT

0260

SPIEN

—

SPISIDL

—

—SPIROV

—

SPITBF

SPIRBF

0000

SPI2CON1

0262

—

DISSCK

DISSDO MODE16

SMP

CKE

SSEN

CKP

MSTEN

SPRE<2:0>

PPRE<1:0>

0000

SPI2CON2

0264

FRMEN

SPIFSD

FRMPOL

—

FRMDLY

—

0000

SPI2BUF

0268

SPI2 Transmit and Receive Buffer Register

0000

Legend:

x = unknown value on Reset, — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT80C51RA2-3CSUL

IC 8051 MCU ROMLESS 40DIP

AT80C31X2-SLSUM

IC 8031 MCU ROMLESS 44PLCC

AT80C31X2-SLSUL

IC 8031 MCU ROMLESS 44PLCC

213300-2

CONN JACKSCREW PLUG 34 POS

AT80C31X2-RLTUM

IC 8031 MCU ROMLESS 44VQFP

AT80C31X2-RLTUL

IC 8031 MCU ROMLESS 44VQFP

AT80C31X2-3CSUM

IC 8031 MCU ROMLESS 40DIP

AT80251G2D-SLSUM

IC 8051 MCU ROMLESS 44PLCC

相关代理商/技术参数

AT80C51RA2-RLRUL

功能描述:8位微控制器 -MCU RLESS RA 40MHZ 3V COM TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT80C51RA2-RLSIV

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:High Performance 8-bit Microcontroller

AT80C51RA2-RLTCL

制造商:IRF 制造商全称:International Rectifier 功能描述:High Performance 8-bit Microcontroller

AT80C51RA2-RLTCV

制造商:IRF 制造商全称:International Rectifier 功能描述:High Performance 8-bit Microcontroller

AT80C51RA2-RLTIM

制造商:IRF 制造商全称:International Rectifier 功能描述:High Performance 8-bit Microcontroller

AT80C51RA2-RLTUL

功能描述:8位微控制器 -MCU RLESS RA 40MHZ 3V COM TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT80C51RA2-RLTUM

功能描述:8位微控制器 -MCU RLESS RA 40MHZ 5V COM TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT80C51RA2-SLRUL

功能描述:8位微控制器 -MCU MICRO RLESS RA 40MHZ 3V COM TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT